Installation Guide Revision-d July 2024 Manual for Firmware Rev-1.10

# Tower LCC+Q

LCC (Layout Command and Control 16 line Input Output board Plus STL Logic

This PDF is designed to be read on screen, two pages at a time. If you want to print a copy, your PDF viewer should have an option for printing two pages on one sheet of paper, but you may need to start with page 2 to get it to print facing pages correctly. (Print this cover page separately.)

## **Table of Contents**

| Overview                                        |    |  |  |  |

|-------------------------------------------------|----|--|--|--|

| STL Editor                                      |    |  |  |  |

| 1 About LCC                                     | 6  |  |  |  |

| 1.1 Some Definitions                            | 6  |  |  |  |

| 1.1.1 Node                                      |    |  |  |  |

| 1.1.2 Segment                                   | 7  |  |  |  |

| 1.1.3 Line                                      |    |  |  |  |

| 1.1.4 Consumer (Output Function)                | 7  |  |  |  |

| 1.1.5 Producer (Input Function)                 |    |  |  |  |

| 1.1.6 Sample Mode                               |    |  |  |  |

| 2 Tower LCC+Q Features                          |    |  |  |  |

| 2.1 Electrical Specifications                   |    |  |  |  |

| 3 Line Details.                                 |    |  |  |  |

| 3.1 Consumer (Output Function)                  |    |  |  |  |

| 3.1.1 The Output Line                           |    |  |  |  |

| 3.1.2 Drive Polarity:                           |    |  |  |  |

| 3.1.3 Delay:                                    |    |  |  |  |

| 3.1.4 Action:                                   |    |  |  |  |

| 3.2 Producer (Input Function)                   |    |  |  |  |

| 3.2.1 The input line                            |    |  |  |  |

| 3.2.2 Input Trigger:                            |    |  |  |  |

| 3.2.3 Delay                                     |    |  |  |  |

| 3.3 Sample Mode                                 |    |  |  |  |

| 4 Power and Serial Connections                  |    |  |  |  |

| 4.1 CAN LCC® Compatible Connector               |    |  |  |  |

| 4.2 Power Connections                           |    |  |  |  |

| 4.3 Status Indicators                           |    |  |  |  |

| 4.4 Blue/Gold Buttons and LEDs.                 |    |  |  |  |

| 4.4.1 Setting up Virtual Code Lines             |    |  |  |  |

| 4.5 Tower LCC+Q I/O Connector Wiring            |    |  |  |  |

| 5 Getting Started                               |    |  |  |  |

| 5.1 CDI (Configuration Description Information) |    |  |  |  |

|                                                 |    |  |  |  |

| 5.2 Input/Output Configuration                  |    |  |  |  |

| 5.3 Identification                              |    |  |  |  |

| 5.4 Node Identification                         |    |  |  |  |

| 5.5 Line (I/O Ports)                            |    |  |  |  |

| 5.5.1 Lines                                     |    |  |  |  |

| 5.3.4 Commands                                  |    |  |  |  |

| 5.3.5 Indications                               |    |  |  |  |

| 5.3.6 Tower LCC+Q Secondary Messages            |    |  |  |  |

| 6 Tower LCC+Q STL Logic Overview                |    |  |  |  |

| 6.1 Statement List (STL) for the Tower LCC+Q    |    |  |  |  |

| 6.1.0 Preface                                   |    |  |  |  |

| 6.1.1 Purpose                                   |    |  |  |  |

| 6.1.2 Basic Knowledge Required                  |    |  |  |  |

| 6.1.3 Segment: Conditionals                     |    |  |  |  |

| 6.2 The Language                                |    |  |  |  |

| 6.2.1 The Operator Statement                    | 26 |  |  |  |

| 6.2.2 The Variables                                             |    |

|-----------------------------------------------------------------|----|

| 6.2.3 The Compilation cycle                                     | 28 |

| 6.2.4 The program cycle                                         | 30 |

| 6.2.5 The Status Word                                           | 30 |

| 6.3 Bit Logic Instructions                                      | 31 |

| 6.3.1 Overview of Bit Logic Instructions                        | 31 |

| 6.3.2 Boolean bit logic operators:                              | 32 |

| 6.3.3 Nesting expressions:                                      | 33 |

| 6.3.4 Statement termination:                                    | 35 |

| 6.3.5 Change the Result of Logic Operation (RLO):               | 36 |

| 6.3.6 Edge transition:                                          | 37 |

| 6.4 Logic Control                                               |    |

| 6.4.1 Overview of Logic Control Instructions                    |    |

| 6.4.2 The Jump Instructions                                     |    |

| 6.5 Logic Variables                                             |    |

| 6.5.1 Overview of different STL variable types                  | 42 |

| 6.5.2 Logic Operation                                           | 43 |

| 6.5.3 Segment: Logic Inputs                                     |    |

| 6.5.4 Segment: Logic Outputs                                    |    |

| 6.5.5 Segment: Track Receiver                                   |    |

| 6.5.6 Segment: Track Transmitter                                |    |

| 6.5.7 Memory Variables                                          |    |

| 6.5.8 Timer Variables                                           |    |

| 6.5.9 Timer details                                             |    |

| 6.6 STL Logic Operators                                         |    |

| 6.6.1 Supported instruction Mnemonics                           |    |

| 7 Track Circuits                                                |    |

| 7.1 Simulating a Code Line with Events                          |    |

| 7.2 Linking Virtual Code Lines                                  |    |

| 7.3 Prototype Code Line                                         |    |

| 8 ABS and APB Signal plus other examples                        |    |

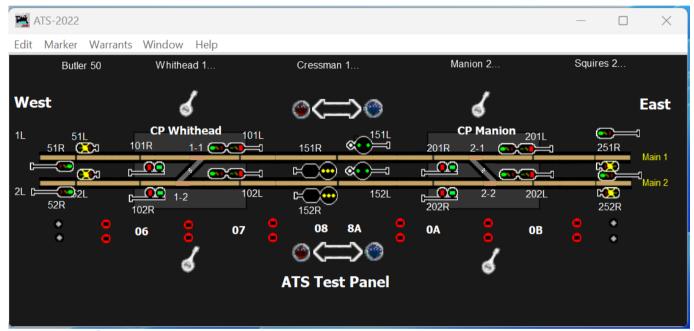

| 8.1 LCC Demo Lavout                                             | 56 |

| 8.2 Entering the Logic Inputs (I0.0 – I15.7)                    | 57 |

| 8.3 Entering the Logic Outputs (Q0.0-Q15.7)                     | 59 |

| 9 Tower LCC+Q compatible Input/Output Cards                     |    |

| 9.1 BOD-4 (DCC Block Occupancy Detector - 4 block plus 4 I/O)   | 60 |

| 9.2 BOD4-CP (DCC BOD 4 block, 4 Inputs, plus 2 turnout drivers) | 60 |

| 9.3 BOD-8 (DCC Block Occupancy Detector - 8 block)              |    |

| 9.4 OIB-8 (Opto Isolator Board - 8 input)                       |    |

| 9.5 SCSD-8 (Single Coil Solenoid Driver)                        |    |

| 9.6 SMD-8 (Stall Motor Driver - 8 line)                         |    |

| 9.7 RB-4 (Relay Board - 4 x SPDT)                               |    |

| 9.8 RB-2 (Dual DPDT Relay Board)                                |    |

| 9.9 BOB-S (Break Out Board - Screw Terminal)                    |    |

| 10 Trouble shooting                                             |    |

| 10.1 Sanity Test                                                |    |

| 10.2 Activity Test.                                             |    |

| 11 Boot Loader                                                  |    |

| 11.1 Boot Loader Upgrade                                        |    |

| 11.2 Firmware Upgrade.                                          |    |

| 12 Grounding and Isolation | 67 |

|----------------------------|----|

| 13 Warranty Information    |    |

| 14 FCC Information         |    |

## **Overview**

The Tower LCC+Q (Layout Command & Control) interface provides a simple and easy way to connect between the NMRA LCC® CAN bus and the layout. The Tower LCC+Q may be connected at any convenient point on the NMRA LCC® CAN bus.

LCC® is a registered trademark of the NMRA. www.nmra.org

## **STL Editor**

Beginning with JMRI test release 5.9.1 there is an **STL Editor** tool available. It is found under the LCC/OpenLCB drop down entry.

One advantage of the STL Editor tool is that it allows you to create and edit your logic using your own JMRI user names instead of the STL map entry shortcut values. (e.g. Control-Point-42R-Diverging:Clear instead of Q2.4)

Another advantage is a selection list of all supported logic operators and their descriptions to make it easy to enter properly formatted logic statements.

The STL Editor can operate interactively with a node, or else save text copies of the data for offline editing.

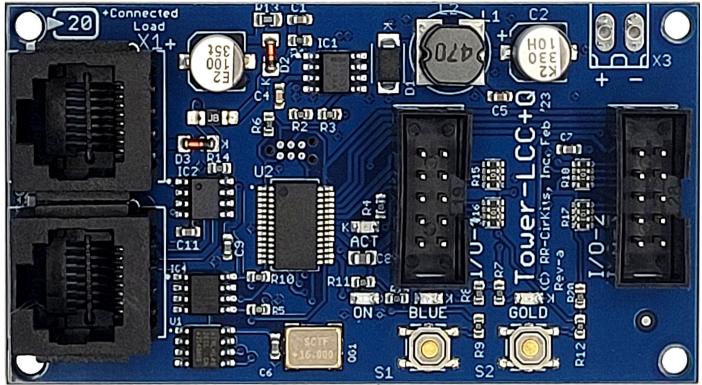

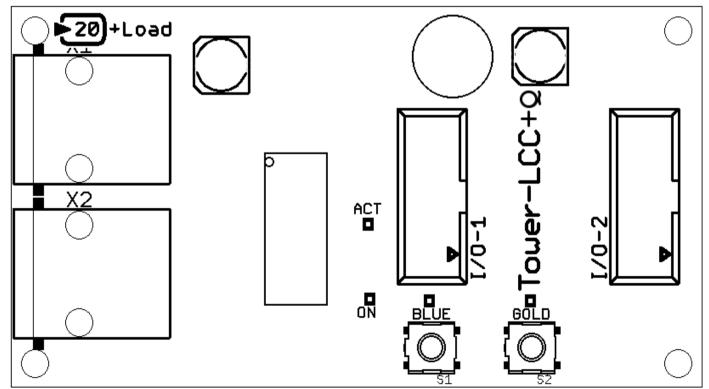

Tower LCC+Q Image

Tower LCC+Q Connectors

# 1 About LCC

The NMRA LCC® is a subset of the OpenLCB specifications created by the OpenLCB group for Layout Command and Control. http://www.openlcb.org/

NMRA LCC® devices are controlled by events. Each event has a unique value that will never be repeated by any other LCC® event in use anyplace on your system, nor even on anyone else's system. The only meaning given to any specific event is that which you give it.

This event uniqueness is a key differences between the LCC and legacy systems. You can always create a link between any two points in the LCC world without needing to know anything else about the system. No more address conflicts, no more dedicating addresses to specific hardware, no more address space size limits.

The LCC uses 64 bit numbers to represent events, (18,446,744,073,709,551,615 possibilities) so we are not planning to run out of event numbers anytime soon. Events are created by event 'Producers' and used by event 'Consumers'. The same event may be created by one or more Producers, and may be used by any number of Consumers. (or none at all)

Events happen, they are not states nor the status of indicators. The only memory of events past exist in hardware. An event can tell you to turn a light 'on'. A different event can tell you to turn a light 'off'. Different events can tell you to turn the same light 'on'. However there is no event that tells you that the light is 'on'. That is a state, and only resides in the hardware that controls the light, or hardware that watches the state of the light. In this node we call these memory items 'Variables', and they are used to store the information about layout items (actual or imaginary) for use at some later time. In order to do logic operations The Tower LCC+Q node includes groups of internal memory items (called Variables) to remember the states that have resulted from the various past EventIDs.

## 1.1 Some Definitions

## 1.1.1 Node

We use the term 'Node' to indicate a single device or board that has both an electrical and logical connection to an LCC network. Some nodes may have multiple logical connections to the network, but only count as one node because there is only a single electrical connection. (transceiver) Some devices may have an electrical connection to the network, but not interact with the LCC logically in any way. An example might be a Repeater. It is electrically connected, but other nodes can not interact with it in any way. It does not count as an LCC node, but must be accounted for when counting the number of devices on a segment.

Please note that this may not be exactly the same usage of the term 'node' as is documented in the NMRA LCC specifications.

## 1.1.2 Segment

On a CAN based LCC network there are electrical limitations on the total number of devices connected to the same cable, or 'Segment'. These limitations take several forms. Electrical limits may be overcome by the use of a repeater.

- **Electrical current limits.** The CAT5 cable used has a limitation of 1A per conductor. The user is responsible to assure that sufficient power is supplied to the cable to supply all nodes within 20' of a power injection point without exceeding this amount. Each node is marked with the amount of current required or supplied to assist the user in this calculation. Be sure to count external loads such as signal lamps, etc.

- **Propagation delay.** The speed of any CAN network is inversely proportional to its total length. The LCC CAN network was chosen to run a maximum of 1000′/300m at 125K bits per second. This is a good compromise for most layouts.

- **Length.** The maximum cable length of 1000′/300m is reduced by 20′/6m for each physical node attached to the segment. This limits any segment to about 48 nodes. The maximum cable length is also shortened by the use of a Repeater due to the delay inherent between segments.

- **Topology.** Each CAN segment should be a single serial string of nodes with a termination at each end. Short branches are allowed, but they count as double their length when subtracted from the segment total. This *required* termination serves both as the current source for a '0' bit, and the cable termination to prevent prevent signal distortion.

In the CDI itself each major section is also called a "Segment". This use of the word has nothing at all to do with the electrical segment discussed above. It is simply a way to divide different (normally related) portions of the CDI from each other to make it simpler to deal with.

## 1.1.3 Line

Each Tower LCC+Q contains 16 I/O lines. Each line has the ability to watch for 6 events (consumers) and to send out 6 events. (producers) Each line has two registers. One register remembers the 'State' of the line. (on or off) The second register remembers the state of the 'Veto' option. The veto option allows or disallows some of the events used to control or respond to the line.

## 1.1.4 Consumer (Output Function)

The Output Functions are called **Consumers**, because they "Consume" or "Read" messages to tell them what to do. The Output Line may be configured in 5 ways. The hardware has an internal function generator that may be configured to create different types of actual outputs.

## **Output Type:**

- **None** (the output line is disabled)

- **Steady** (output line follows the output state),

- **Pulse** (output line alternates one time when the output state is first 'on'),

- **Blink A** (output line alternates on/off while output state is 'on').

• **Blink B** (output line alternates off/on while output state is 'on').

#### **Drive Polarity:**

- **Low (0V)** The output line is low when true. (default)

- **High (5V)** The output line is high when true.

#### **Delay:**

The function generator also includes delay settings for both 'on' and 'off' transitions. These same delays are used to control the blink rate and pulse length, or to simply delay the output action for some interval after the controlling event is seen. (e.g. to simulate "running time" on a CTC panel)

#### Action:

Each consumer event can be configured to control the line's output or veto register state in one of 9 ways:

- None

- **On** (Line Activate), **Off** (Line Inactivate)

- **Change** (Toggle)

- **Veto on** (Active), **Veto off** (Inactive)

- Gated On (Non Veto Output), and Gated Off (Non Veto Output)

- **Gated Change** (Non Veto Toggle)

The consumer events may also control a Veto state. If the veto state is 'on', then the consumer 'Gated on' (activate) and 'Gated off' (inactivate) events are ignored.

The producer 'on' (non vetoed input), and 'off' (non vetoed input) are also ignored (blocked) when the veto state is 'on'.

## 1.1.5 Producer (Input Function)

The Input functions are called **Producers** because when they are activated they "Produce" or "Create" messages in response to their activity.

The input line may be configured in 3 ways:

- **None** is no response.

- Normal response is used when an input change directly controls the sending

of events.

- **Alternating** action is used when a single line needs to produce alternating control events. (e.g. turnout normal, reverse)

Each producer event can be configured to trigger in one of 10 ways:

- None

- **Input On**, **Input Off**, allow you to create events simply based on a change of the input line. This is the normal use for a producer.

- Gated On (Non Veto Input), Gated Off (Non Veto Input), allow events to respond to, or ignore, any input changes based on the veto state. For example this would allow you to enable/disable fascia buttons for local control of a turnout by using the output events from a panel switch to control the veto.

- **Cascade** is the trigger option that allows you to create a new producer event based on the commands to both activate and inactivate the output state. E.g. to cascade a yard ladder. (Cascade combines the following two commands)

- Output State On Command (activate), Output State Off Command (inactivate), are trigger options that allow you to create a new producer event based on the command to activate or inactivate the output. E.g. to cascade a yard ladder.

- Output On (function hi), Output Off (function lo), create a new event when the output of the function generator changes. This might be used to build a realistic traffic light controller. Be careful with this option because it can create a lot of traffic continuously, especially if the function output is blinking rapidly.

The 'on'-'off' time delays are used as function output delay or input debounce delay depending on the line status.

## 1.1.6 Sample Mode

Sample mode is used for Berrett Hill Touch Toggles or other dual mode situations where the input and output states of a line may not necessarily be the same. In Sample mode the line is normally driven by its output state, but it briefly disables the output drive and reads the un-driven (pull-up) state of the line. The input must be current limited for the case where the input and output are not the same. The normal output load must also be tolerant of brief changes during the input sample interval. The output must not load the line with more than 10K to prevent the load from causing false inputs.

Sample mode is automatically enabled if both output and input functions are enabled on the same line. Several different I/O modules are now compatible with Sample mode. This allows you to connect both input modules and output modules at the same time on the same port. This can save costs by combining dissimilar functions on the same hardware.

# 2 Tower LCC+Q Features

- The Tower LCC+Q uses the CAN bus implementation of the NMRA LCC.

- Communicates over the LCC CAN bus at 125Kb.

- Support for a total of 16 Input/Output lines:

- Up to 16 Input Lines. (internal pull-up termination on all lines)

- Up to 16 Output Lines. (these are the same physical lines as the inputs)

- Internal Logic Engine with up to 4096 characters of logic space.

- Support for up to 16 virtual code lines. (8 aspects per Track Circuit)

- CDI (Configuration Description Information) controlled configuration via Software.

- Lines may be configured as individual input, output, or shared, (sampled) lines.

- Automatically saves input/output and logic states during power down.

- Boot Loader allows contact less user firmware upgrades over the LCC® (Layout Command & Control) connection.

- Power is supplied over the LCC® bus. The TowerLCC requires 20mA. plus whatever load may be imposed by the I/O modules that you choose.

- Efficient switcher regulated 5VDC is available on each I/O port connector to power external modules or lamps.

## 2.1 Electrical Specifications

#### I/O Port 1:

Pin 1 - 5 volt logic level at 25mA.

Pin 2 - 5 volt logic level at 25mA.

Pin 3 - 5 volt logic level at 25mA.

Pin 4 - 5 volt logic level at 25mA.

Pin 7 - 5 volt logic level at 25mA.

Pin 8 - 5 volt logic level at 25mA.

Pin 9 - 5 volt logic level at 25mA.

Pin 10 - 5 volt logic level at 25mA.

#### I/O Port 2:

Pin 1 - 5 volt logic level at 25mA.

Pin 2 - 5 volt logic level at 25mA.

Pin 3 - 5 volt logic level at 25mA.

Pin 4 - 5 volt logic level at 25mA.

Pin 7 - 5 volt logic level at 25mA.

Pin 8 - 5 volt logic level at 25mA.

Pin 9 - 5 volt logic level at 25mA.

Pin 10 - 5 volt logic level at 25mA.

Maximum current to be supplied by all I/O lines combined is 200mA. This 200mA total limit means that not over 8 lines may supply their maximum current at any one time.

# 3 Line Details

## 3.1 Consumer (Output Function)

#### 3.1.1 The Output Line

The hardware has an internal function generator that may be configured in 5 ways to create different types of actual outputs:

- **None** (the output line is disabled)

- **Steady** (output line follows the output state),

- **Pulse** (output line alternates one time when the output state is first 'on'), the pulse to either high or low level is based on the timing delay intervals, then return to normal. Delay 'Interval 1' sets the time delay before the pulse occurs, and delay 'Interval 2' sets the pulse length itself.

- **Blink A** (output line alternates on/off while output state is 'on'). Normally used to control devices such as crossing gate flashers directly from the output lines. 'A' and 'B' are the two phases of the flashing. Blink A or Blink B refers to which phase starts the action.

- **Blink B** (output line alternates off/on while output state is 'on'). Delay 'Interval 1' sets the length of phase A, and delay 'Interval 2' sets the length of phase B. Normally it will be more realistic to use the LED drivers available on a Signal LCC node that can also add in the proper fade effects.

## 3.1.2 Drive Polarity:

- **Low (0V)** The output line is low when true. (default)

- **High (5V)** The output line is high when true.

## 3.1.3 Delay:

The function generator also includes delay settings for both 'on' and 'off' transitions. These same delays are used to control the blink rate and pulse length, or to simply delay the output action for some interval after the controlling event is seen. (e.g. to simulate "running time" on a CTC panel)

#### 3.1.4 Action:

Each consumer event can be configured to control the line's output or veto register state in one of 9 ways:

- None

- **On** (Line Activate), **Off** (Line Inactivate)

- Change (Toggle)

- **Veto on** (Active), **Veto off** (Inactive)

- Gated On (Non Veto Output), and Gated Off (Non Veto Output)

- **Gated Change** (Non Veto Output)

In addition to controlling the Output state, the consumer events may also control a Veto state. If the veto state is 'on', then the consumer 'Gated on' (activate) and 'Gated off' (inactivate) events are ignored.

The producer's 'on' (non vetoed input), and 'off' (non vetoed input) are also ignored (blocked) when the veto state is 'on'.

## 3.2 Producer (Input Function)

#### 3.2.1 The input line

An input line may be configured in 3 ways:

- **None** is no response to the input.

- Normal response is used when an input change directly controls the sending of events.

- Alternating action is used when a single line needs to produce alternating control events. (e.g. turnout normal, reverse)

## 3.2.2 Input Trigger:

Each producer event can be configured to trigger in one of 10 ways:

- None

- **Input On, Input Off,** allow you to create events simply based on a change of the input line. This is the normal use for a producer.

- Gated On (Non Veto Input), Gated Off (Non Veto Input), allow events to respond to, or ignore, any input changes based on the veto state. For example this would allow you to enable/disable fascia buttons for local control of a turnout by using the output events from a panel switch to control the veto.

- **Cascade command**, Combines the 'Output State On' and 'Output State Off' commands to always send the selected EventID if the consumer for this line is activated or deactivated. This is a shortcut to cascade a yard ladder.

- Output State On Command (activate), Output State Off Command (inactivate), are trigger options that allow you to create a new producer event based on the command to activate or inactivate the output. This is used to specify a cascaded command in a single direction.

- Output On (function hi), Output Off (function lo), create a new event

when the output of the function generator actually changes. This might be

used to build a realistic traffic light controller. Be careful with this option

because it can create a lot of traffic continuously, especially if the function

output is blinking rapidly.

#### 3.2.3 **Delay**

Each line includes two delay timers that are used to control blinks, pulses, and input debounce times.

Interval 1 controls the 'on' delay or time, and Interval 2 controls the 'off' delay or time. The count may be set from 0-60,000 and the

base interval may be set to Milliseconds, Seconds, or Minutes. This allows for delays from 1ms. to over 41 days. Probably the extremes will never be required, but this gives you a good range to choose from. Actual accuracy is  $\frac{1}{2}$ % or better. Millisecond times are calculated to the nearest 8 ms.

Retrigger allows the time interval to be reset if the line state is set to 'true' again prior to the end of the delay time.

If the line state is set to 'false' prior to the end of the delay time, then the output does not occur.

The same timers are used for both input and outputs, so there are some combinations that are not allowed.

## 3.3 Sample Mode

Sample mode is used for Touch Toggles or other dual mode situations where the input and output states of a line may not necessarily be the same. In Sample mode the line is normally driven by its output state, but it briefly disables the output drive in order to read the un-driven (pull-up) state of the line.

The restrictions are:

- Any input must include a 1K series resistor to prevent shorting out any output that may be active at the same time.

- Any output must not load the line with more than a 10K load to prevent the load from creating a false input.

- Also note that the output function must be tolerant of the brief sample times when the output may change state during the sample period.

Sample mode is automatically enabled if both output and input functions are enabled on the same line. Several different RR-CirKits I/O modules are now compatible with Sample mode. This allows you to connect both input modules and output modules at the same time on the same port. This can save costs by combining dissimilar functions on the same hardware. (e.g. occupancy and turnout control)

# **4 Power and Serial Connections**

The Tower LCC+Q (16 Line I/O Board) has four connectors and four status indicators. Two of these connectors are for connections to the LCC bus network. The other two are used as connections to the I/O lines. This section covers the system connections consisting of the CAN bus port connectors, power connections, I/O port connections and Status indicators.

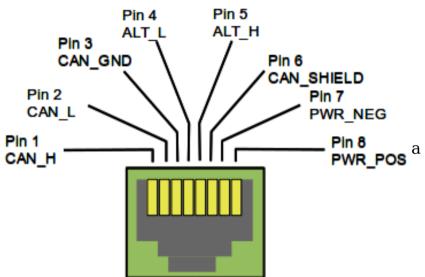

## 4.1 CAN LCC® Compatible Connector

The data connection is made to the Tower LCC+Q via a standard RJ-45 CAT5 cable connected to either of the two RJ-45 connectors. The LCC wiring passes straight through both connectors.

The LCC specification requires minimum of 1' of cable length between connectors. Slightly shorter cables (10") should not significantly impact operation.

These cables are commonly sold for wired Ethernet use.

#### Pin outs for the CAN LCC RJ-45 data connector:

| Pin | Description          |  |  |  |

|-----|----------------------|--|--|--|

| 1   | CAN H                |  |  |  |

| 2   | CAN L                |  |  |  |

| 3   | CAN GND              |  |  |  |

| 4   | Alt L (DCC negative) |  |  |  |

| 5   | Alt H (DCC positive) |  |  |  |

| 6   | GND                  |  |  |  |

| 7   | GND                  |  |  |  |

| 8   | +Power 12-27V        |  |  |  |

LCC power is supplied on Pin 7 and Pin 8. Power can be from +12VDC to +27VDC. The RR-CirKits LCC Power-Point delivers approximately 15VDC to the bus.

The LCC connectors accept standard Ethernet style CAT5 (or better) cables. 4 pair cables are required by the Tower-LCC+Q. For any but the smallest networks it is recommended that you choose AWG 24 CAT-5 wiring or AWG 23 CAT6 wiring. The use of AWG 26 wiring reduces the maximum length of your network to approximately 40% of its specified length. Especially avoid using copper clad aluminum wire or AWG 28 low profile wiring as they have even higher than normal resistance at the relatively low frequencies used by the LCC. This higher resistance shortens the maximum distance for reliable communications even more than using AWG 26 wiring does.

A note on connectors: RJ-45 crimp connectors are made with three blade styles. (the end of the contact that crimps into/onto the wire) Single 'U', double 'UU', and triple 'VVV' points. Stranded cables may be made with any of the three blade styles because the points crimp into and between the individual wire strands. However if you are using solid wire, then you must only use the three point style of blade. ('VVV') It is designed to trap the solid wire between the three points, two on one side, and the center one on the other side, for a corrosion tight connection. The single or double pointed blades will simply press against the side of the solid

wire, and will fail in time. (usually the

morning of your open house)

## 4.2 Power Connections

The Tower LCC+Q requires an external power source of between 7.5 and 27 volts DC from the LCC cable.

The LCC Power-Point unit is a convenient way to supply the required power to the Tower LCC+Q and other LCC boards over standard RJ45 cables.

LCC Power-Point shown with Terminator

Each segment of LCC® cable requires a terminator at each end. Power can also be supplied by other powered LCC modules, or with the RR-CirKits LCC Repeater.

## 4.3 Status Indicators

The Tower LCC+Q has two status indicators located near to the LCC connectors. The green ON status indicator shows the power status of the Tower LCC+Q itself. The red ACT (activity) indicator normally shows all data activity on the bus, and also any activity/error status during a boot loader firmware upgrade. (see section 10.0)

## 4.4 Blue/Gold Buttons and LEDs

A limited amount of configuration may be accomplished on some manufacturer's nodes by using the Blue and Gold push buttons and indicators. The primary use is to link up producer and consumer lines. The Tower LCC+Q does not support this option.

The Gold LED can indicate two different error messages. If it is flashing (10% duty cycle) it indicates that it is idling in forced boot loader mode. If the Gold LED is blinking (50% duty cycle) it indicates that the board was unable to initialize itself on the network, most likely because it could not establish an alias.

## 4.4.1 Setting up Virtual Code Lines

Use the CDI tools to setup links. The EventID for the TX code set will always come from the transmitting node and be entered into the receiving node to avoid accidental reuse of EventID numbers from setup to setup.

Each node can setup one or more virtual code lines to any other node. For simplicity these virtual links are named 'Circuit Y0', 'Circuit Y1', etc. It is incumbent upon the user to keep track of which 'Coded' virtual links are created between nodes. Be sure to record which block (0-15) is used for each side of the virtual links if you have not standardized these connections. There is no need to use the same 'block' number on both sides of any virtual coded track circuits, and in fact they will not normally be matching. Normally these virtual links will follow along with the rails, but there is no actual requirement that they do so.

Each track circuit links the logic with one out of a group of eight line states. Normally these are used to represent the track speed allowed at arrival to the next mast. This is based on the 'Aspect' shown by the mast.

## 4.5 Tower LCC+Q I/O Connector Wiring

The two port connector's wiring is as follows. Note that the pin numbers and I/O line numbers are NOT the same, and actually run opposite to each other.

| Pin number | Connection name | Image                                 |

|------------|-----------------|---------------------------------------|

| 1          | line 8          | Wire , 10                             |

| 2          | line 7          | 1 N 1 N 1 N                           |

| 3          | line 6          |                                       |

| 4          | line 5          | 4   ω   4   ω                         |

| 5          | Ground          | +                                     |

| 6          | +5VDC           |                                       |

| 7          | line 4          | υ σ <u>-</u> υ σ -                    |

| 8          | line 3          | 784784                                |

| 9          | line 2          | ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ |

| 10         | line 1          | Tracel Wile I                         |

10 position IDC cable numbering and description

# **5 Getting Started**

To properly display the Tower LCC+Q CDI you will need to use JMRI DecoderPro 5.6 or later <a href="http://www.jmri.org/">http://www.jmri.org/</a> to configure the Tower LCC+Q. This "point and click" interface will save you much time and frustration while setting the many possible options that you will need to configure, and in fact are the only way that we suggest for configuring the Tower LCC+Q node.

**Node Address:** Each Tower LCC+Q has a single node address that is used for CDI programming on the layout. Each individual Tower LCC+Q has its node address imprinted on a label on the back side of the board. It is recommended that you name your node with a friendly user name as the first step in configuration.

## 5.1 CDI (Configuration Description Information)

The CDI is the tool used to access the LCC node's internal configuration options. Instead of relying on printed manuals or volunteer created files to present the various decoder options, (like DCC devices have for the past 20 years) the LCC specification expects the manufacturer of the LCC node itself to present its capabilities and options in a standardized manner from an internal file. This allows any LCC configuration tool to be used interchangeably, and not need to be updated

to support new hardware or firmware upgrades.

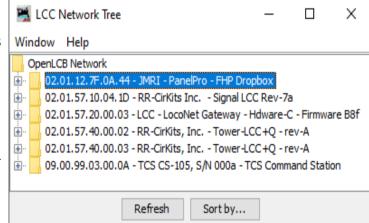

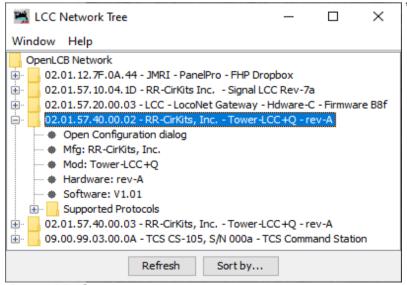

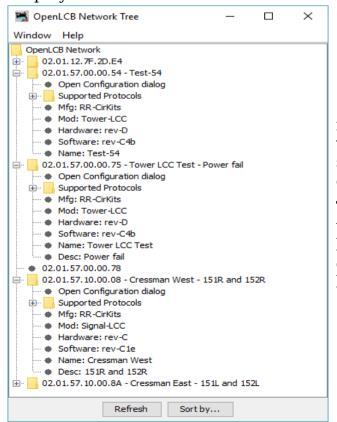

**Start** up the CDI tool. Once the tool is monitoring the LCC network you will be presented with a list of nodes similar to this.

The list should include all the nodes that are currently visible on your LCC network. In this example the first entry in the list (02.01.12.7F.0A.44) is the configuration program itself as seen through the interface.

วพ

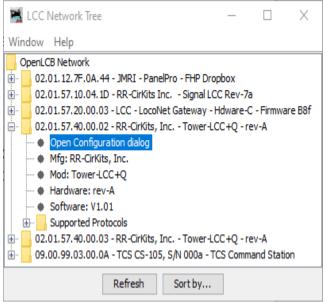

**Select** the node that you desire to configure and click on its '+' to open it. This will open up further options for that node. In this example there are various options including 'Open Configuration dialog' and a list of 'Protocols Supported'.

Note: This node shows V1.01 firmware and should be upgraded immediately before further configuration is done!

Open Node

The Node Information will help you to be sure that you have chosen the correct node.

With the JMRI CDI program you simply highlight an item to open it in a new window.

**CDI** is the supported Protocol that you will need for configuration purposes.

Remember that with the LCC this display information is provided by the manufacturer and stored in the node itself rather than in some piece of paper, external file or program.

Once the CDI window opens up you can modify its contents by using the 'Refresh' and 'Write' buttons found near to each item.

The **Refresh** button will present a new, unused, default value if one has not been previously stored.

There is also a '**Refresh All**' button located at the bottom of the window. This will reload all the EventID current values from the device's internal storage.

The **Write** button will store the currently displayed value or selection into the

Open the JMRI CDI Window

Highlight 'Open Configuration dialog' to

Deepsoft CDI Window

node's memory. If you have changed any value you must always then do a 'Write' to store it into the node before it can take effect.

The JMRI CDI tool will highlight the entry with orange until it has been written to the board. This is a helpful reminder that the change has not yet been stored into the board where it can take effect.

## 5.2 Input/Output Configuration

We suggest that the user take advantage of the JMRI CDI tool or a similar program to set the Tower LCC+Q configuration values.

The following examples are using the JMRI CDI tool for the Tower LCC. Select the 'LCC' drop down list and click on 'Configure Nodes'. When the node selection window opens, choose the node to configure, click on 'Open Configuration dialog'.

This will open the CDI tool and automatically read in the basic information for the node.

This information is presented in a tabular format to allow a reasonably compact display but still allow easy access to the vast amount of configuration information.

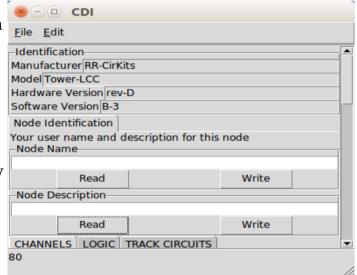

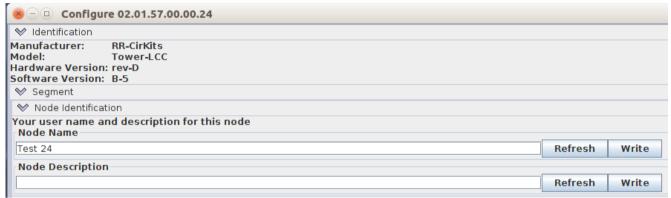

## 5.3 Identification

The first section shown will be the **Identification**. It includes the manufacturers

JMRI CDI Window

name and node model plus any version information.

## 5.4 Node Identification

The next item is the **Node Identification**. It contains the Name and Description that you give to the node. The name of this example node is 'TEST 24'. This name will appear in the node selection window to make it easier to select the correct node for configuration. There is a 63 character limit to the node name and description items.

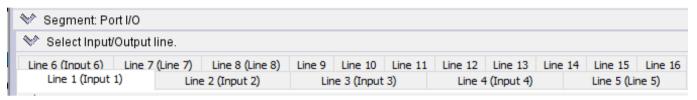

## 5.5 Line (I/O Ports)

The Tower LCC+Q has two 8 bit Input/Output ports for a total of 16 lines. To be compatible with the various RR-CirKits I/O modules, each port is normally configured to be either all Inputs, or all Outputs. However each line may also be individually set as either input or output for special purposes.

For the special case of one wire I/O a line may even be configured as both input and output at one time. (Sample Mode section 1.2) The Berrett Hill Touch Trigger is an example of a one line device. The Tower LCC+Q can also control both the indicator's color, using consumers, and report the output, using producers in the same channel.

Any special effects may be applied differently for each line. E.g. one line may be held steady while another sends a pulse or is blinking.

## 5.5.1 Lines

Each I/O line is called a 'Line' and is selected by tabs and presented separately. Note that lines 1-8 appear on Port 1, and lines 9-16 appear on Port 2 of the node.

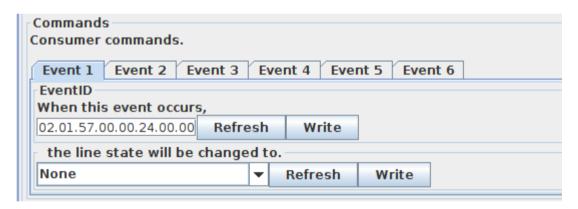

## 5.3.4 Commands

Commands are consumer events that are sent to the line. A command can directly control the line, for example by turning it on or off. A command may also indirectly control the line, for example by controlling its veto status. Each line has 6 consumer events associated with it. Each Consumer event is associated with a single task or action.

For example event 1 could be used to turn an output 'on', and event 2 could be used to turn an output 'off'. The consumer events are:

- None -

- On (Line Active) Sets the output state to 'true'

- Off (Line Inactive) Sets the output state to 'false'

- Change (Toggle) Changes the output state to its opposite state

- **Veto On (Active)** Sets the veto state to 'true'

- Veto Off (Inactive) Sets the veto state to 'false'

- Gated On (Non Veto Output) Sets the output state to 'true' if veto is 'false'

- Gated Off (Non Veto Output) Sets the output state to 'false' if veto is 'false'

- Gated Change (Non Veto Output) Inverts the output state if veto is 'false'

The last three items probably need some clarification. An event set to 'On' will always set the output state to 'true'. However an event set to 'Gated On' will only set the output to 'true' if the veto state is 'off'. If the veto state is 'on' then the three 'Gated' events are ignored, and the line does not change state.

For example when a CTC operator controls a turnout he would send the events configured as 'On' and 'Off'. However a local operator button would send the (different) events configured as 'Gated On' and 'Gated Off'. The CTC operator could then send a 'Veto On' event that would block the local operator from controlling the turnout, but still allow normal operation from his own panel. Then the CTC operator could send a 'Veto Off' event that would re-enable the local operator's control over the turnout.

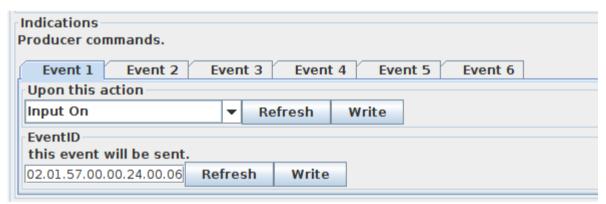

## 5.3.5 Indications

Indications are producer events that are sent to the bus. Each line has 6 producer events associated with it.

Each Producer event is associated with one action. For example event 1 could be used to indicate that the input line is changed to 'active', and event 2 could be used to indicate that the input line is changed to 'inactive'. The consumer events are:

- **None** This event is not created in response to anything.

- Input On Responds to an input level change to 'true'

- **Input Off** Responds to an input level change to 'false'

- Gated On (Not Veto Input) Gated response to an input level change to 'true'

- Gated Off (Not Veto Input) Gated response to an input level change to 'false'

- Cascade command Responds to any output state change

- Output State On command Responds to an output state change to 'true'

- Output State Off command Responds to an output state change to 'false'

- Output On (Function hi) Responds to an output level change to 'high'

- Output Off (Function lo) Responds to an output level change to 'low'

## 5.3.6 Tower LCC+Q Secondary Messages

In these examples there are no second or third messages being sent in the sense of our previous LocoNet products. However additional messages may be sent or responded to if desired by utilizing unused events. For example to activate a 'Next' turnout whenever the 'first' turnout event is sent, (in order to sequence a yard ladder) you could use the 'Cascade command' to send an event to the next turnout in the ladder. These additional messages, if enabled, are sent whenever the primary event occurs. Another simple example would be to allow two or even three different messages to be sent when ever a single button is pressed. For example a single event could be used as the master reset for many turnouts simply by adding it as an additional 'On' or 'Off' event to each turnout in the group.

# 6 Tower LCC+Q STL Logic Overview

The logic contained in the Tower LCC+Q is a major departure from our previously available logic. In the past we included some simple conditional logic that could be configured by filling in boxes or selecting options from a list. This was useful, and powerful enough to do basic signaling. However it was not capable of creating generic logic statements, nor even complex signal logic without needless repetition.

To get around these restriction we have completely eliminated the previous conditional based logic and replaced it with a simplified version of STL (Statement List) logic.

For those folks already familiar with STL, we have removed all temporal functions. In other words we can not count, do math, nor do any analog operations. We can preset timers to fixed values, but we can not change timer values based on the result of logic operations. (other than by choosing between different timers)

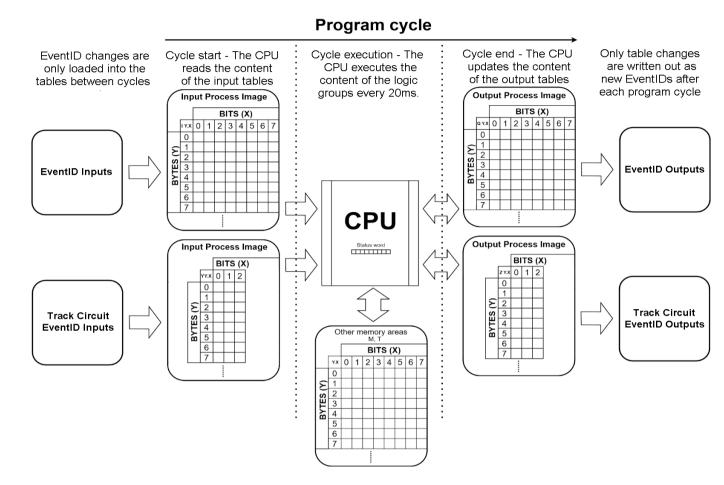

We have also intentionally restricted any program branching (Jumps, Go-to, etc.) to only be allowed in the forward direction. This prevents the creation of any loops, both intentional or accidental. The logic itself steps through its statement list every 20mS recalculating each logic statement found in the current path. If a recalculation results in a change from a previous state, then that change is used to create one or more EventIDs representing the new logic state.

## 6.1 Statement List (STL) for the Tower LCC+Q

The STL for the Tower LCC+Q is a subset of the Siemens S7-x language.

## 6.1.0 Preface

In addition to its 16 I/O lines, and virtual track code lines, the Tower LCC+Q also includes 32 logic operator groups. This logic is state driven, not event driven. To interface the logic with LCC EventIDs we provide two tables to convert Inputs and Outputs into their corresponding events. The STL logic may be used to create signaling logic or other animations such as control of grade crossings. It may also be used to create NX (eNtry Exit) routing.

## 6.1.1 Purpose

This section of the manual is your guide to creating user programs in the Statement List programming language STL.

The manual also includes a reference section that describes the syntax and functions of the language elements of STL.

## 6.1.2 Basic Knowledge Required

The manual is intended for Tower LCC+Q programmers, operators, and maintenance/service personnel.

In order to understand this manual, general knowledge of automation technology is required.

In addition to, general computer literacy and the knowledge of other working equipment similar to the PC and the operating systems MS Windows, Apple macOS, or Linux, a copy of JMRI 5.6 or later is required to configure this system.

This consumer grade hardware and software is not intended to be used in any part of a safety-critical system.

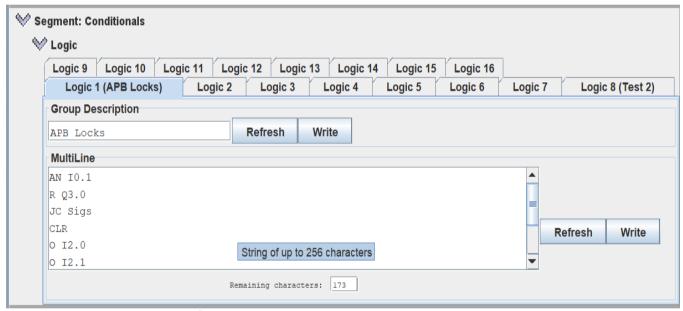

## 6.1.3 Segment: Conditionals

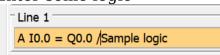

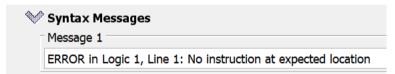

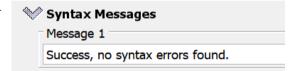

The various logic operators are entered into the segment **Conditionals**. The logic is broken up into 16 logic groups. Each group contains a block of text called a 'MultiLine'. Each MultiLine has room for 256 characters. This is a total of 4,096 characters of text based logic. The only syntax related to the individual line endings is that the comment operator '//' is automatically closed at the end of each line of the MultiLine. Comment operators '/\*' and '\*/' may be used within a line.

Entering text into a MultiLine.

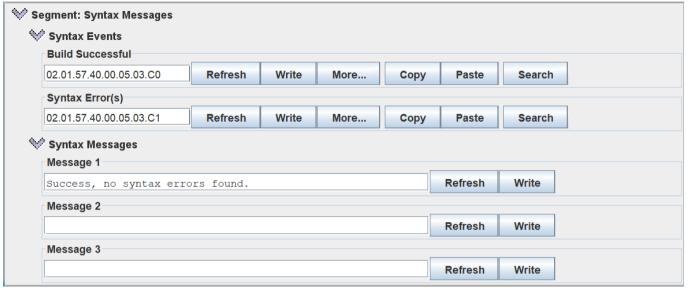

In the example above we see a number of operators and variables grouped on individual lines. This is done for clarity and not required. Lines will automatically wrap if too long for the space. Once you have completed the compilation cycle (see section 6.2.3) you will see the following error code in the syntax messages. (In this case there are no errors) If there is an error in Message 1, then be sure to also check for additional errors in Message 2, and Message 3. Only the first three errors are shown as messages.

Example error message.

These error messages only check for proper syntax, with no compilation errors. You are responsible for entering the correct logic.

## 6.2 The Language

The Tower LCC+Q programming language is based on a subset of the IEC 1131 IL (Instruction List) standard as used by Siemens in their STL language. This subset does not include any of the counters, variables (other than Boolean) nor any math functions, (i.e. no variables that require other than true/false values) that are normally included by Siemens in their version of STL.

Like any other PLC (Programmable Logic Controller) programming language, IL languages have both benefits and drawbacks. One of the clearest benefits is program execution speed. (efficiency) As with assembly language in general, instruction lists are a low overhead language and execute faster than graphical languages. Another plus is that ILs also tend to take up less memory space. These are both clear benefits, especially in a device that is tight on memory space like an LCC node, and is the primary reason that we have chosen it. The Siemens STL is even more compact than ILs in general.

On the downside, STL is not that common of a language, mainly because so many people tend to prefer visual programming languages and environments. As a result it is becoming less common for industrial PLC equipment.

## 6.2.1 The Operator Statement

Like many other programming languages, STL logic has a limited set of allowed operations. These are typically short hand for the logic operations that you need to perform. Some examples are 'O' for 'OR', 'A' for 'AND', 'N' for 'Not', etc.

Each logic statement is started off directly with a logic operation. (A, O, or X) This may seem a bit strange to those familiar with other languages, but this shorthand is done to save the extra 'Load' command that would be required if the 'Load' was not implied. Also with this format, the statement may be a continuation from a previous statement using the previous RLO. (Result of Logic Operation) In order to accomplish this, the previous RLO must be have been saved in the BR register by using the 'SAVE' command before it is terminated.

Each statement is terminated with an '=' (Assign), 'R' (Reset), or 'S' (Set) command. Unless a 'SAVE' command has been done, the logic value (RLO) will have been cleared and the next statement will begin anew.

## 6.2.2 The Variables

To simplify the logic processing the various logic variables are saved in arrays, or images in memory. Because we limit ourselves to boolean logic, each variable only requires one bit of storage space in these images. Of course the LCC EventIDs are much larger than this. This compression is possible because each logic entry only has access to the values stored in this node. Any outside references require assigning an EventID pair to each item (bit) in the image. Inputs are controlled by Consumers, and each Output change will Produce matching EventIDs.

You must assign all required input and output variables to matching locations in the input and output variable tables prior to their use. Unused table entries do not cause any issues. The 'M' (Memory) variables are used for temporary (intermediate)

Selecting the EventIDs for Input Variable 10.0

storage of results, and have no associated LCC EventIDs, nor do they create any network traffic.

There are 128 possible input (I) variables and 128 possible output (Q) variables available on the Tower LCC+Q. These are grouped together 8 at a time simply for naming convenience. They are actually stored as blocks of 16 bytes.

On PLC equipment the numbering corresponds to actual input and output lines, but that would be very limiting in our event driven environment where events can be to/from anyplace in the network, not just physical I/O lines on a single node. In addition to the I and O variables, we have also added 'Y' and 'Z'

Selecting the EventIDs for Output Variable Q0.0

variables in order to transmit groups of speed information variables between signal masts. (16 input groups, (Y) and 16 output groups. (Z)

Note: You may not Assign, nor Set/Reset, the logic value of an 'Input' variable, nor may you use LCC EventIDs to modify an 'Output' variable. These variables represent the actual hardware inputs and outputs of a PLC which have a fixed direction, either as inputs or outputs.

## 6.2.3 The Compilation cycle

Before the logic statements you have entered can be used in the logic engine they need to be pre-processed into a form that can be used efficiently. For example you may have entered a jump label that is called "SAVE:". The instruction "SAVE" is the one that saves the logic value from one statement for use by the next statement. We must be able to distinguish between these different functions. The compile process creates a table of locations in the final logic that act as targets for any jump instructions, then removes their names from the list. This prevents them from being confused with one another.

Another job of the compiler process is to remove all white space from the list, and remove all comments.

Yet another job is to interpret the timer set commands and change them into actual timing values for use by the timers.

Probably the most useful thing that the Compilation cycle does is to check that you have used the proper syntax for your logic. Obviously it can not tell you if your logic is correct, but it will check that you have entered variables for your operations, that you have closing parens that match your opening ones, etc.

The compile process is run automatically each time the node is booted. The first few errors are written to messages in the Segment: 'Syntax Messages'. Two EventIDs are also created, one for 'Build Successful' and the other for 'Syntax Error/s' To read the resulting messages you must first click on [Refresh] for each message.

#### For example:

1. Enter some logic

- 2. [Write] it to the node.

- 3. Click on [More...]  $\rightarrow$  [Reboot] to trigger the compile process.

4. Click [Refresh] for Message 1 to see the result.

4. The error is someplace in Logic 1, Line 1. An investigation reveals that the 'Comment' operator needs to be '//' not just a single '/'. Correct this and redo steps 2. - 4. to see the results.

## 6.2.4 The program cycle

Note: 'Input' variables (I, Y) are only modified by LCC EventIDs, and 'Output' variables (Q, Z) only create EventIDs. Both types of variables (plus M and T) may be used in logic evaluations.

## 6.2.5 The Status Word

The Status Word is an internal register used to keep track of the state of the instructions as they are being processed. In order to use STL more effectively it is important to understand the Status Word and its functions. However for most basic logic operations you do not need to worry about the status word. It will hide behind the curtain and take care of itself.

Each bit in the Status Word has a specific function to keep track of bit logic (RLO, STA), and whether the logic should continue, be nested or start anew (/FC, OR, BR).

## The Most Important Status Word Bits

#### /FC - Not First Check

If the /FC bit is a 0 then the instruction is considered to be the first instruction being processed in a statement. If the /FC is a 1 then the instruction being scanned will use the logic value from the previous instruction. Certain instructions like =, S

and R will set the /FC bit to 0, thus automatically starting a new logic statement after it. Other instructions like A or O will set the /FC bit to 1 signaling that you need to combine the current logic status with the next instruction.

#### **RLO - Result of Logic Operation**

The **RLO** bit stores the running logic state of the currently processing instructions. Certain bit logic and comparison instruction will turn the RLO to a 1 when the condition is TRUE and write a 0 when the condition is FALSE. Other instructions read the RLO (=, S, R) to determine how they are to execute.

#### **STA - Status**

The **STA** bit reflects the state of the current Boolean address being processed.

## **Aditional Status Word Bits**

#### OR

The **OR** bit is used for combining AND functions before OR functions.

#### **BR** - Binary Result

The Binary Result transfers the result of the operations (RLO) on to the next instruction for reference. When the **BR** bit is 1 it enables the output of the block to be TRUE and thus allow other blocks after it to be processed. The SAVE, JCB and JNB instructions set the BR bit. This allows you to jump to another location in the logic and continue the logic evaluation from there.

## **6.3 Bit Logic Instructions**

#### 6.3.1 Overview of Bit Logic Instructions

#### **Description**

Bit logic instructions work with just two digits, 1 and 0. These two digits form the base of a number system called the binary system. The two digits 1 and 0 are called binary digits or bits. In the world of contacts and coils, a 1 indicates activated or energized, and a 0 indicates not activated or not energized. Typical Inputs could be block detectors or fascia contacts. Typical Outputs could be turnout positions or signal aspects.

The bit logic instructions interpret these values of 1 and 0 and combine them according to Boolean logic. These combinations produce a result of 1 or 0 that is called the "result of logic operation" (**RLO**), and is usually assigned to an output or stored in a memory location once the logic statement is evaluated.

These signal states are stored in arrays or process maps for easy access by the logic engine. LCC consumers (Inputs) store their updated state in the Input (I) map area any time they are seen. LCC producers watch the Output (Q) map and send the appropriate EventID any time the output map value changes.

In this manner the STL logic is kept synchronized with the current layout status.

#### 6.3.2 Boolean bit logic operators:

In these descriptions '<Bit>' represents the bit variable in the process map being tested or set by the logic operator. 'RLO' stands for Result of Logic Operator. In other words it represents the result of any previous operations, and is used as the input to this example. A (red highlight) simply shows the operator position in this example. '/\*' and '\*/' are the open and close comment markers respectively.

#### A - And

◆ Format

A <Bit>

Description

**A** checks whether the state of the addressed bit is "1", and ANDs the test result with the RLO.

◆ Example

```

RLO /* Previous */ \mathbf{A} I1.1 /* AND with Input var1.1 */ = \mathbf{Q4.0} /* Assign the result to Output var4.0 */

```

#### AN - And Not

◆ Format

AN <Bit>

◆ Description

**AN** checks whether the state of the addressed bit is "0", and ANDs the test result with the RLO.

◆ Example

```

RLO /* Previous */ AN I1.1 /* AND with NOT Input var1.1 */ = Q4.0 /* Assign the result to Output var4.0 */

```

#### O - Or

◆ Format

**O** <Bit>

◆ Description

**O** checks whether the state of the addressed bit is "1", and ORs the test result with the RLO.

Example

```

RLO /* Previous */ \circ I1.1 /* OR with Input var1.1 */ = Q4.0 /* Assign the result to Output var4.0 */

```

#### ON - Or Not

◆ Format

ON <Bit>

◆ Description

**ON** checks whether the state of the addressed bit is "0", and ORs the test result with the RLO.

```

Example

```

```

RLO /* Previous */ ON I1.1 /* OR with Input NOT var1.1 */ = Q4.0 /* Assign the result to Output var4.0 */

```

#### X - Exclusive Or

◆ Format

**X** <Bit>

◆ Description

**X** checks whether the state of the addressed bit is "1", and XORs the test result with the RLO.

You can also use the Exclusive OR function several times in succession. The final result of the logic operation is "1" if an odd number of checked addresses are "1".

**♦** Example

```

RLO /* Previous */ \mathbf{X} I1.1 /* XOR with Input var1.1 */ = \mathbf{Q4.0} /* Assign the result to Output var4.0 */

```

#### XN - Exclusive Or Not

◆ Format

XN <Bit>

◆ Description

**XN** checks whether the state of the addressed bit is "0", and XORs the test result with the RLO.

◆ Example

```

RLO /* Previous */ XN I1.1 /* XOR with Input NOT var1.1 */ = Q4.0 /* Assign the result to Output var4.0 */

```

#### 6.3.3 Nesting expressions:

#### A( - And with Nesting Open

◆ Format

A(

◆ Description

**A(** (AND nesting open) saves the RLO and OR bits and a function code into the nesting stack. A maximum of seven nesting stack entries are possible..

Example

```

RLO /* Previous */ A ( O I1.2 O M0.3) /* AND with Group (O Input 1.2 O Memory 0.3) */ = Q4.0 /*Assign the RLO to Output 4.0 */

```

## AN( - And with Nesting Open

◆ Format

AN(

Description

**AN(** (AND NOT nesting open) saves the RLO and OR bits and a function code into the nesting stack. A maximum of seven nesting stack entries are possible..

Example

```

RLO /* Previous */ AN( O I1.2 O M0.3) /* AND with NOT Group (O Input 1.2 O Memory 0.3) */ = Q4.0 /*Assign the RLO to Output 4.0 */

```

#### O( - Or with Nesting Open

◆ Format

0(

◆ Description

**O(** (OR nesting open) saves the RLO and OR bits and a function code into the nesting stack. A maximum of seven nesting stack entries are possible..

Example

```

RLO /* Previous */ \bigcirc ( O I1.2 O M0.3) /* OR with Group (O Input 1.2 O Memory 0.3) */ = Q4.0 /*Assign the RLO to Output 4.0 */

```

#### ON( - Or Not with Nesting Open

◆ Format

ON(

◆ Description

**ON(** (Or nesting open) saves the RLO and OR bits and a function code into the nesting stack. A maximum of seven nesting stack entries are possible..

◆ Example

```

RLO /* Previous */ ON ( O I1.2 O M0.3) /* OR with NOT Group (O Input 1.2 O Memory 0.3) */ = Q4.0 /*Assign the RLO to Output 4.0 */

```

#### X( - Exclusive Or with Nesting Open

◆ Format

X(

Description

**X(** (XOR nesting open) saves the RLO and OR bits and a function code into the nesting stack. A maximum of seven nesting stack entries are possible..

Example

```

RLO /* Previous */ X( O I1.2 O M0.3) /* XOR with Group (O Input 1.2 O Memory 0.3) */ = Q4.0 /*Assign the RLO to Output 4.0 */

```

#### XN( - Exclusive Or Not with Nesting Open

◆ Format

XN(

Description

**XN(** (XOR NOT nesting open) saves the RLO and OR bits and a function code into the nesting stack. A maximum of seven nesting stack entries are possible..

Example

```

RLO /* Previous */ XN ( O I1.2 O M0.3) /* X OR with Not Group (Input 1.2 Or Memory 0.3) */ = Q4.0 /* Assign the RLO to Output 4.0 */

```

#### ) - Nesting Closed

◆ Format

Description

) (nesting closed) removes an entry from the nesting stack, restores the OR bit, interconnects the RLO that is contained in the stack entry with the current RLO according to the function code, and assigns the result to the RLO. The OR bit is also included if the function code is "AND" or "AND NOT".

Statements which open parentheses groups:

- A ( And with Nesting Open

- AN ( And Not with Nesting Open

- o( Or with Nesting Open

- ON ( Or Not with Nesting Open

- x ( Exclusive Or with Nesting Open

- xn ( Exclusive Or Not with Nesting Open

- ◆ Example

```

RLO /* Previous */ ) A M1.1 /* Close Group, AND with Memory 1.1 */ = Q4.0 /* Assign the RLO to Output 4.0 */

```

#### 6.3.4 Statement termination:

- = Assian

- ◆ Format

- = <Bit>

- Description

- = **<Bit>** writes the content of the RLO into the addressed bit. You may make multiple assignments of the RLO in the same statement.

- ◆ Example

```

RLO /* Previous */ = Q4.0 = Q4.1 = M1.0 */ Assign the RLO to Output 4.0, Output 4.1, and Memory 1.0 */

```

- R Reset

- ◆ Format

- R <Bit>

- ◆ Description

**R** (reset bit) places a "0" in the addressed bit if the RLO = 1.

Example

```

R M1.1 /* Reset Memory 1.1 to 0. (False) */

```

#### S - Set

- ◆ Format

- **s** <Bit>

- Description

- **S** (set bit) places a "1" in the addressed bit if the RLO = 1.

- Example

```

S M1.1 /* Set Memory 1.1 to 1. (True) */

```

Note: There is an important distinction between '=', 'S', and 'R'. The 'Assign' forces the output to follow the result of the logic at each recalculation. The 'S' or 'R' only change the output as the logic result first changes.

## 6.3.5 Change the Result of Logic Operation (RLO):

#### NOT - Negate RLO

Format

NOT

Description

**NOT** negates the RLO.

Example

```

NOT /* invert the RLO */ = M1.1 /* Assign RLO to Memory 1.1 */

```

#### **SET - Set RLO (=1)**

Format

**SET**

Description

SET sets the RLO to signal state "1".

```

Example SET /* set the RLO to "1" (True) */ = M1.1 /* Assign RLO to Memory 1.1 */

```

#### CLR - Clear RLO (=0)

Format

**CLR**

Description

**CLR** sets the RLO to signal state "0".

Example

```

CLR /* clear the RLO to "0" (False) */ = M1.1 /* Assign RLO to Memory 1.1 */

```

#### SAVE - Save RLO in BR Register

Format

**SAVE**

Description

**SAVE** saves the RLO into the BR bit. The first check bit /FC is not reset. For this reason, the status of the BR bit is included in the AND logic operation in the next network.

The use of SAVE and a subsequent query of the BR bit in the same block or in secondary blocks is not recommended because the BR bit can be changed by numerous instructions between the two. It makes sense to use the SAVE instruction before exiting a block because this sets the ENO output (= BR bit) to the value of the RLO bit and you can then add error handling of the block to this.

```

• Example

```

```

SAVE /* save the RLO for use in the next statement */

```

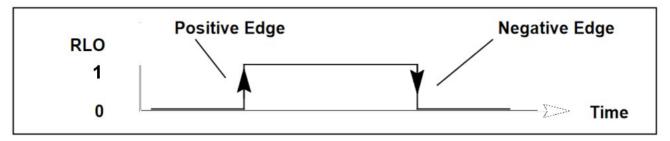

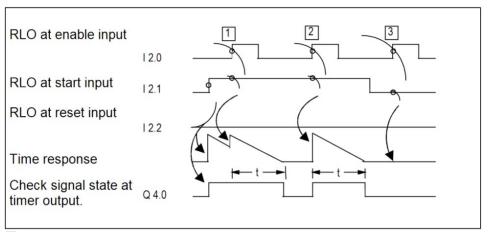

#### 6.3.6 Edge transition:

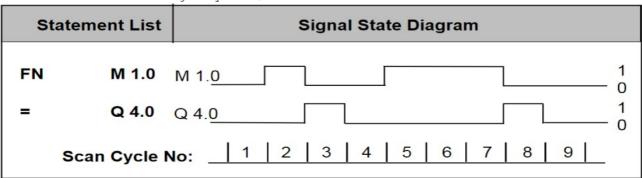

#### FN - Edge Negative

Format

FN <bit>

Description

**FN** <**Bit**> (Negative RLO edge) detects a falling edge when the RLO transitions from "1" to "0", and indicates this by RLO = 1.

During each program scan cycle, the signal state of the RLO bit is compared with that obtained in the previous cycle to see if there has been a state change. The previous RLO state must be stored in the edge flag address (<Bit>) to make the comparison. Usually a Memory variable is used for this purpose, like M 1.0 in the example below. If there is a difference between current and previous RLO "1" state (detection of falling edge), the RLO bit will be "1" after this instruction

#### Definition

#### • Example

If the programmable logic controller detects a negative edge at input M 1.0, it energizes the output at Q 4.0 for one program scan cycle. (20mS)

**FN M 1.0** /\* When a Negative edge is detected at Memory 1.0 \*/ = Q4.0 /\* Output 4.0 is set to true for one logic cycle \*/

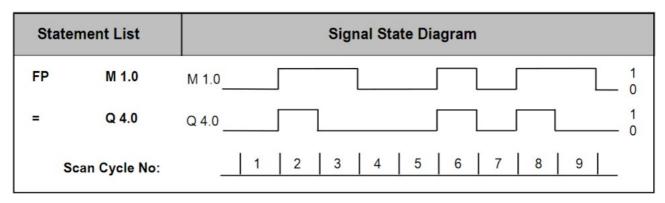

#### FP - Edge Positive

Format

FP <bit>

Description

**FP <Bit>** (Positive RLO edge) detects a rising edge when the RLO transitions

from "0" to "1", and indicates this by RLO = 1.

#### • Example

If the programmable logic controller detects a positive edge at input I 1.0, it energizes the output at Q 4.0 for one program scan cycle. (20mS)

**FP M 1.0** /\* When a Positive edge is detected at Memory 1.0 \*/ = Q4.0 /\* Output 4.0 is set to true for one logic cycle \*/= Q4.0

FP M1.1 A I 0.1 S Q1.1

// The RLO will go true if Input 0.1 is positive when the positive edge of Memory 1.1 happens. If so, then Output Q 1.1 will be set to true;

// If Input 0.1 is negative, when the positive edge of Memory 1.1 happens, then the RLO will remain negative. and nothing happens.

### **6.4 Logic Control**

## **6.4.1 Overview of Logic Control Instructions**

#### **Description:**

You can use the Jump instructions to control the flow of logic, enabling your program to interrupt its linear flow to resume scanning at a different point.

The address of a Jump instruction is a **label**. A jump label may be as many as four characters, and the first character must be a letter. Jump labels are followed with a mandatory colon ":" and must precede the program statement in the line being jumped to. (the jump label must not be somewhere in the middle of a logic string) We intentionally restrict any jump instructions to be in a forward direction in the logic to prevent accidental endless looping.

Note: Please note that the jump destination must always be located at the beginning of a statement line in the MultiLine. Also the jump destination must never be placed in the middle of a logic statement.

### 6.4.2 The Jump Instructions

You can use the following jump instructions to interrupt the normal flow of your program unconditionally:

#### JU - Jump Unconditional

Format

#### JU <jump label>

Description

**JU <jump label>** interrupts the linear program scan and jumps to a jump destination, regardless of the status word contents. The linear program scan resumes at the jump destination. The jump destination is specified by a jump label. Only forward jumps are possible by design to prevent looping.

Example

```

JU EXIT /* Jump Unconditional to EXIT. */ APPR: SET Q 1.1 /* The Intermediate Operations are ignored */ EXIT: /* Operations continue at EXIT: */

```

The following jump instructions interrupt the flow of logic in your program based on the result of a logic operation (RLO) produced by the previous instruction statement:

#### JC - Jump if RLO=1

• Format

#### JC <jump label>

Description

If the result of logic operation is 1, **JC <jump label>** interrupts the linear program scan and jumps to a jump destination. The linear program scan resumes at the jump destination. The jump destination is a specified jump label. Only forward jumps are possible.

If the result of logic operation is 0, the jump is not executed. The RLO is set to 1, and the program scan continues with the next statement.

Example

```

RLO /* Previous True */ JC STOP /* If RLO is true Jump Conditional to STOP: */

AN I 1.2 /* If RLO was false continue at */ JC APPR /* Jump Conditional to

APPR: */

STOP: SET Q 1.0 JU EXIT /* Set aspect to Stop then Exit */

APPR: SET Q 1.1 /* Set aspect to Approach then Exit */

EXIT:

```

#### JCN - Jump if RLO=0

Format

#### JCN <jump label>

Description

If the result of logic operation is 0, **JCN <jump label>** interrupts the linear program scan and jumps to a jump destination. The linear program scan resumes at the jump destination. The jump destination is specified a jump label. Only forward jumps are possible.

If the result of logic operation is 1, the jump is not executed. The program scan continues with the next statement.

#### Example

```

RLO /* Previous NOT True */ JCN APPR /* Jump Conditional to APPR: */

STOP: /* If previous was true */ SET Q 1.0 /* Set aspect to Stop then Exit */

JU EXIT

APPR: SET Q 1.1 /* Set aspect to Approach then continue to Exit */

EXIT:

```

Note the change from the previous example where the conditional had to be inverted before checking in order to check for the inverted sense.

#### JCB - Jump if RLO=1 with BR

Format

#### JCB < jump label>

Description

If the result of logic operation is 1, **JCB <jump label>** interrupts the linear program scan and jumps to a jump destination. The linear program scan resumes at the jump destination. The jump destination is specified by a jump label. Only forward jumps are possible.

If the result of logic operation is 0, the jump is not executed. The RLO is set to 1, and the program scan continues with the next statement.

Independent of the RLO, the RLO is copied into the BR for the **JCB <jump label>** instruction.

• Example AND I 1.0 AND I 1.2 Jump Conditional with BR to STOP:.

```

A I 1.0 A I 1.2 JCB STOP AN I 1.2 JCB APPR //AND NOT I 1.2 Jump Conditional with BR to APPR:

```

STOP: SET Q 1.0 JU EXIT //STOP: Set Q 1.0 Jump Unconditional to EXIT.

APPR: SET Q 1.1 //APPR: Set Q1.1. then EXIT:

EXIT:

#### JNB - Jump if RLO=0 with BR

Format

#### JNB <jump label>

Description

If the result of logic operation is 0, **JNB <jump label>** interrupts the linear program scan and jumps to a jump destination. The linear program scan resumes at the jump destination. The jump destination is specified a jump label. Only forward jumps are possible.

If the result of logic operation is 1, the jump is not executed. The RLO is set to 1 and the program scan continues with the next statement.

Independent of the RLO, the RLO is copied into the BR for the **JNB <jump label>** instruction.

#### • Example

A I 1.0 A I 1.2 JC STOP A I 1.2 JNB APPR //AND | 1.0 AND | 1.2 Jump Conditional to STOP:. AND | 1.2 Jump Conditional Not with BR to APPR:.

STOP: SET Q 1.0 JU EXIT //STOP: Set Q 1.0 Jump Unconditional to EXIT.

**APPR: SET Q 1.1** // APPR: Set Q1.1.

EXIT: //EXIT:

Note the change from the previous example where the conditional had to be inverted before checking in order to check for the inverted sense.

The following jump instructions interrupt the flow of logic in your program based on the signal state of a bit in the status word:

#### JBI - Jump if BR=1

• Format

#### JBI < jump label>

#### Description

If status bit BR is 1, **JBI <jump label>** interrupts the linear program scan and jumps to a jump destination. The linear program scan resumes at the jump destination. The jump destination is specified by a jump label. Only forward jumps are possible.

If the status bit is 0, the jump is not executed. The RLO is set to 1 and the program scan continues with the next statement.

#### Example

A I 1.0 A I 1.2 JBI OVER //AND | 1.0 AND | 1.2 Jump if BR =1 to OVER:

AN I 1.2 SET Q 1.0 JU OVER //AND Not | 1.2 Set Q 1.0 Jump Unconditional to OVER.

OVER:

#### JNBI - Jump if BR=0

• Format

#### JNBI <jump label>

#### Description

If status bit BR is 0, **JNBI <jump label>** interrupts the linear program scan and jumps to a jump destination. The linear program scan resumes at the jump destination. The jump destination is specified by a jump label. Only forward jumps are possible.

If the status bit is 1, the jump is not executed. The RLO is set to 1 and the program scan continues with the next statement.

#### Example

A I 1.0 A I 1.2 JNBI OVER //AND | 1.0 AND | 1.2 Jump if BR = 0 to OVER:

AN I 1.2 SET Q 1.0 JU OVER // AND Not | 1.2 Set Q 1.0 Jump Unconditional to OVER.

OVER:

### 6.5 Logic Variables

Variables as we use the term here refer to individual locations in memory that can store one of two values, true or false. (1/0, on/off, normal/reverse, etc.) In computer science this is called Boolean logic. With the exception of Timers (T) we never give variables any value other than zero and one.

### 6.5.1 Overview of different STL variable types

- I Input (Consumer)

- Q Output (Producer)

- Y Track Receiver

- Z Track Transmitter

- M Local Memory

- T Timer

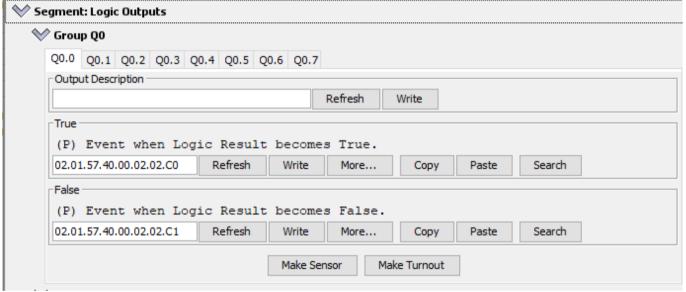

External Input (I) and Output (Q) variables are linked to LCC EventIDs by using two segments of the CDI.

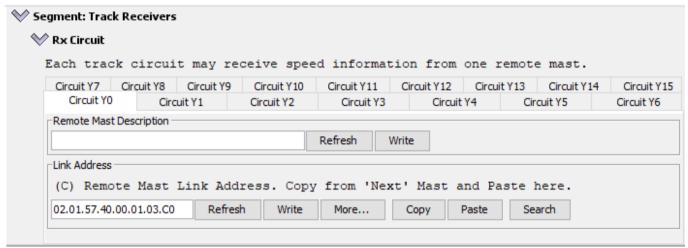

In a similar manner Track Circuit Receivers (Y) and Track Circuit Transmitters (Z) are linked to external Event ID groups by using two segments of the CDI. Each link connects together a group of 8 EventIDs, typically variables from one mast sent to the logic of another adjacent mast.

Local (internal) Memory (M) variables may be used as required in your logic. Because there is no link from memories to external objects there is no need to define them in terms of EventIDs in the CDI. If a 'memory' item is needed in another node, then use 'I' or 'Q' which do link to other locations using EventIDs over the network, or else assign them to to a 'Q' variable as well.

In like manner Timers (T) are directly created in the logic by defining and using them, but are not visible outside of the logic engine. To use them on the network you must assign them to to a 'Q' variable as well to make them visible. Remember that the 'Network' includes I/O lines on this node as well as items on other nodes.

Reminder: You may not Assign, nor Set/Reset, the logic value of an 'Input' variable, nor may you use LCC EventIDs to modify an 'Output' variable. These variables represent the actual hardware inputs and outputs of a PLC which have a fixed direction, either used as inputs or outputs.

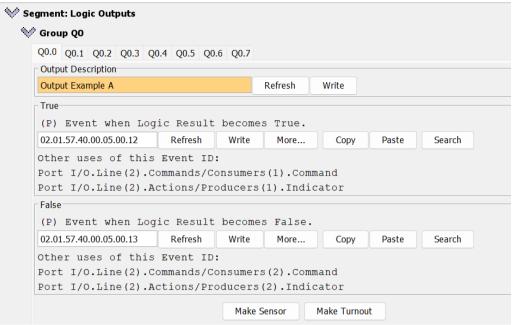

### 6.5.2 Logic Operation

The logic table itself is re-calculated every 20ms on a continuously repeating basis. However Logic Outputs (producers) only result in EventIDs being sent out if they change from their previous state. This logic re-calculation is not dependent upon, nor is it synchronized with any EventIDs changing. This is an important difference between this logic and the previous logic as used in older versions of our RR-CirKits nodes.

One effect of this is that you are not guaranteed to be able to notice brief changes in external events. If an event changes, then is restored in less than 20ms, then the change may be missed entirely by the logic. In a similar manner any change will not be noticed by the logic for as long as 20ms after it appears on the network. Normally in the scale of time used on our layouts this is not an issue, but it is something to be aware of. For example, if you are calculating train direction by using sensor pairs, then the sensors need to be spaced far enough apart to give longer than 20ms between activation at the highest train speeds allowed.

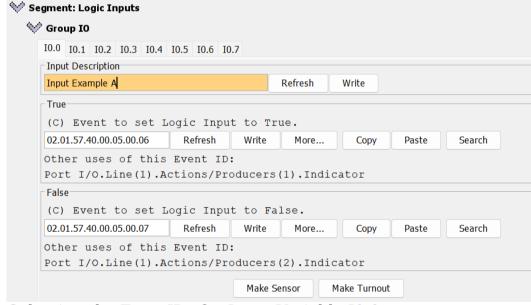

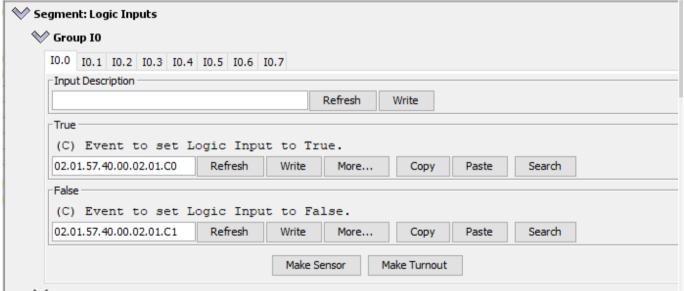

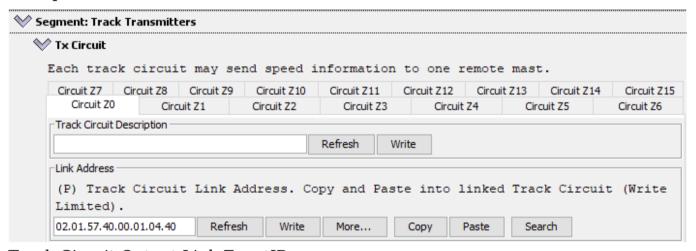

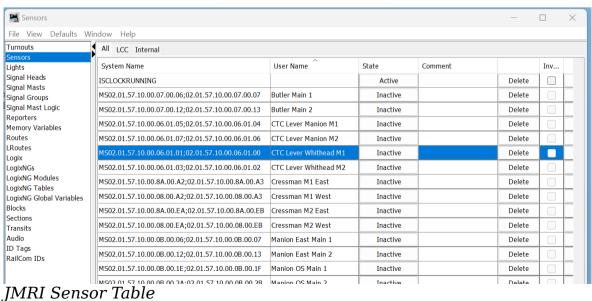

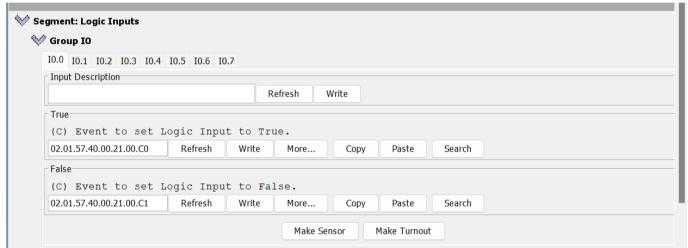

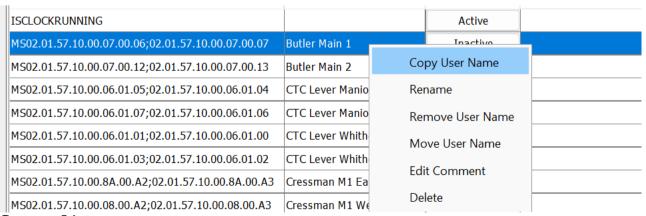

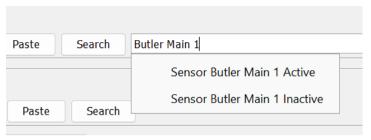

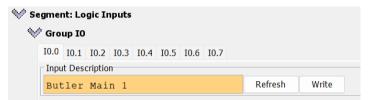

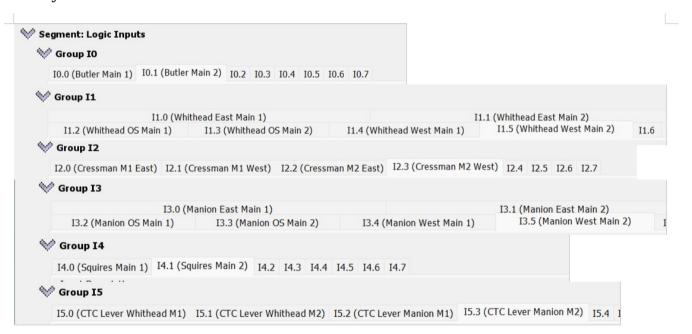

### 6.5.3 Segment: Logic Inputs

The logic inputs (LCC Consumers) take the shorthand form of "I0.0" where each input item is identified by a group number followed by an item number. This shorthand form is what is used in the logic statements when calculating logic functions. Block occupancy sensors, push buttons, and turnout position contacts are some examples of inputs. "I" (input) variables are used for external inputs. You are not allowed to assign (=) values to inputs because they are Consumers only and can not be written back to the network.

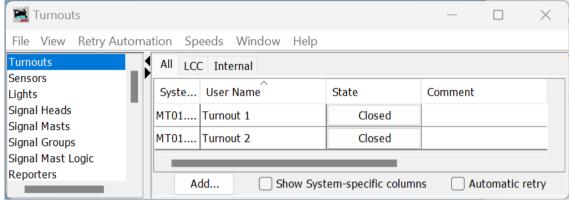

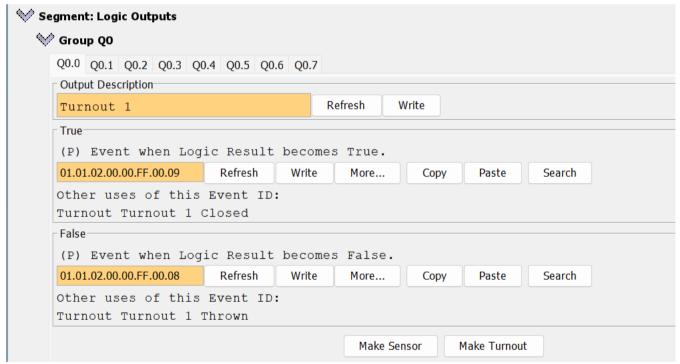

EventIDs into Logic Inputs

Each logic input has two EventIDs associated with it, one to set it 'true' and the other to set it 'false'. It also has the option of assigning a user name, and using the [Make Sensor] or [Make Turnout] to add the item into the [MRI tables.